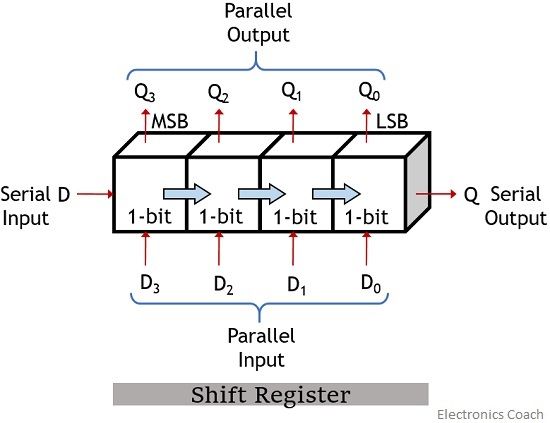

Definition: A shift register is a sequential logic circuit that acts as a unit to store and transfer binary data. Basically shift registers are bidirectional FIFO circuit, that shifts every single bit of the data present in its input towards its output on each clock pulse.

We know registers are the circuits constructed using flip-flops for storing binary data. One-bit of data is stored by each flip-flop at a time. So, the storage of multiple bits of data requires multiple flip-flops.

Thus the storing capacity of the register depends on the number of flip-flops used in its construction.

Shift registers are formed by the serial combination of D flip-flops, where each flip-flop in the arrangement holds single data bit. The serial arrangement permits the output of one flip-flop to act as input to other and this allows the shifting of data bit inside the register.

It is to be noted here that data can be transferred in or out of the register either serially or parallely. So, the data bit movement inside the shift register give rise to various configurations which are as follows:

- SISO: Serial-in Serial-out: It permits the insertion of data serially and taking the output also in a serial manner.

- SIPO: Serial-in Parallel-out: Here the data is inserted serially either from the left or right direction. But the output is taken parallely.

- PISO: Parallel-in Serial-out: This type of shift register allows the parallel input of data bit, but the output is taken serially.

- PIPO: Parallel-in Parallel-out: PIPO shift register permits both in and out of data bit in a parallel manner.

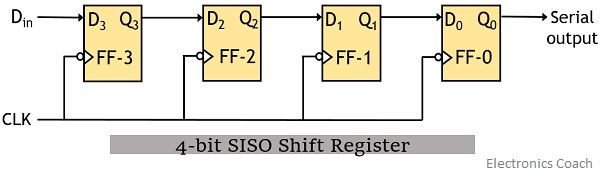

Operation of SISO Shift Register

As we have already discussed that a SISO is a type of shift register in which the input is fed serially and output is also taken in serial manner.

So consider a connection of 4 D flip-flops D0 to D3 as shown in the figure below:

Initially, we consider all the flip-flops are at reset mode. Thus the output of each flip-flop in the arrangement is logic low i.e., 0.

Here we have assumed a shift right mode circuit as the data input is present at the left end while the stored bit is getting shifted towards the right so as to provide serial output.

Let us now understand how data is stored in a shift register.

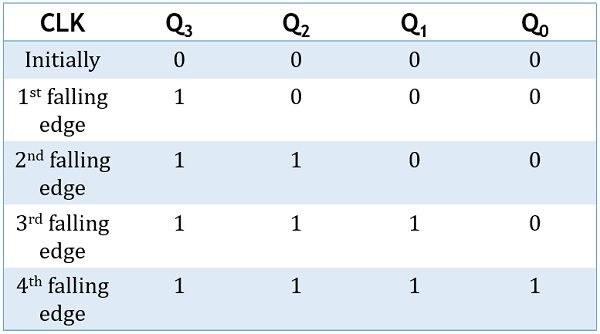

Suppose we have to insert ‘1111’ inside the shift register. Initially, as the device is in reset mode thus the output of each register will be low, thereby providing output of all the 4 registers as 0000.

- Now beginning with LSB of the data to be inserted so 1 is provided as input to the circuit i.e., D3 = 1. But as initially the output of all the flip-flops were 0. Therefore, D2, D1 and D0 will be 0. While input D3 = 1 will cause Q3 to be 1. Thus the overall output will be 1000.

- Further, when another data input bit i.e., 1 is provided at D3. Then again this will cause Q3 to be 1, but as Q3 is provided as input to D2. Therefore, this will cause Q2 to be 1, while rest all other outputs will be 0. Thus for a second falling edge, we will get 11 at the stored bit inside the register, thereby giving the overall output as 1100.

- Similarly, when 3rd input bit ‘1’ is provided then previous output Q2 will cause the input D1 to be 1. This will provide output Q3, Q2 and Q1 as 1 while Q0 will still remain 0. Thus the overall output will be 1110.

- Furthermore, when MSB of the data is provided as input, then 1 at Q1 will cause D0 input to be logic high. So, this will cause Q0 to be 1.

Thus in this way shift register stores ‘1111‘ thereby showing in the output.

The figure below represents the truth table for the 4-bit SISO shift register:

Considering the above table let us have a look at the waveform representation of a SISO shift register:

Here the first figure shows the clock input signal while the second figure shows the data input to be stored which is 1111 for this particular case. Thus we have shown continuous high signal in case of data input.

Also, the above figure represents the 4 data output of the flip-flops.

Initially, all the outputs were 0, this is clearly shown in the waveform representation. However, the output Q3 changes from 0 to 1 on arrival of first clock pulse. While rest other outputs are still 0.

In a similar way, the second clock pulse changes Q2 from 0 to 1. Thus now both Q3 and Q2 are showing logic high in the waveform representation.

So, in this way the above figure is clearly showing the SISO operation of the shift register and on the arrival of 4th clock pulse the output of all the 4 registers will be 1. As the storage is performed by shifting each bit on the arrival of each clock pulse thus it is named so.

Applications of Shift Registers

The different configurations of shift registers provide uses in various fields like a SISO shift register is used to generate time delay in digital circuits. A SIPO shift register can act as serial to parallel converter.

In a similar way, PISO shift register changes parallel input into serial output thereby performing the job of a parallel to serial converter.

Leave a Reply