Definition: The synchronous counter is a type of counter in which the clock signal is simultaneously provided to each flip-flop present in the counter circuit. More specifically, we can say that each flip-flop is triggered in synchronism with the clock input.

Unlike asynchronous counter where separate clock pulses are used to trigger the flip-flop, all the flip-flops in synchronous counters are triggered using a single clock pulse.

We know designing an asynchronous counter is easy then what is the reason behind designing the synchronous counter. The answer to this question is that the asynchronous counter has a limitation towards maximum operating frequency.

Therefore, in order to overcome this limitation, synchronous counters are designed in which simultaneous clocking is provided. Due to simultaneous clocking, the output varies in synchronization with the clock input.

Synchronization leads to variation in each output bit at the same time with a common clock signal. Thereby eliminating the ripple effects and so the propagation delay.

Circuit and Operation of Synchronous Counter

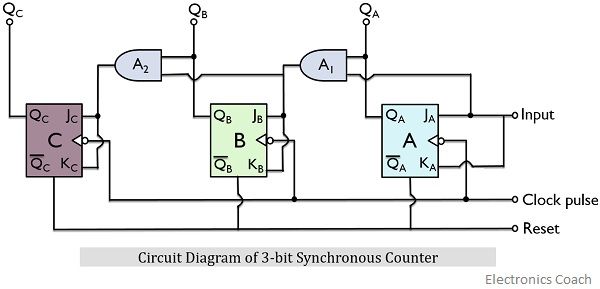

Here the figure below shows a 3-bit synchronous counter:

The circuit is composed of 3 J-K flip-flops and 2 AND gates. And the clock signal to trigger the flip-flop is provided at the same time.

It is noteworthy here that only the input terminal of flip-flop A is provided with active high signal and therefore it toggles at the falling edge of each clock input.

Furthermore, the input to flip-flop B will be provided through an AND gate whose output will depend on the input and output of previous flip-flop i.e., B in this case. And the gate turns on and causes flip-flop B to toggle only when the output of flip-flop A will be high.

In a similar way, the input to flip-flop C will be the output of 2nd AND gate. Therefore, flip-flop C toggles only when gate A2 will be on. And A2 will be on only in case when the output of A1, as well as flip-flop B, will be high.

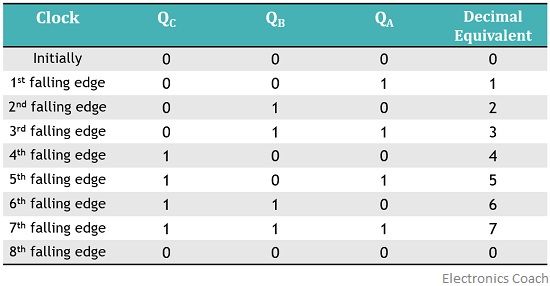

Let us now understand the operation performed by the synchronous counter by considering a 3-bit synchronous counter:

In the beginning, the flip-flops are set at 0, thus the outputs of all the three flip-flops i.e., QCQBQA will be 000. However, at the falling edge of the first clock pulse, the output of flip-flop A toggles from 0 to 1. But no change will occur at the output of flip-flop B and C because the input terminals of these two flip-flops are 0 until the next clock pulse arrives.

Therefore, on applying the first clock pulse, the output of the flip-flops i.e., QCQBQA will be 001.

Now further before the commencement of the 2nd clock pulse, inputs of both the flip-flops i.e., A and B will be 1. This is so because the output of gate A1 is high. So, at the falling edge of the 2nd clock pulse, the output of flip-flop A and B will again toggle.

Therefore, this will lead to a change in the output of flip-flip A, from 1 to 0 and flip-flop B from 0 to 1.

Hence now the output will be 010. Thus this causes the turning off both gate A1 and A2.

Again when 3rd clock pulse is applied, the at its falling edge, again the output of flip-flop A toggles. This causes the turning on of gate A1. And due to this gate A2 will also turn on and therefore the output will be 011.

On moving further when 4th clock pulse is applied, the inputs to all the 3 flip-flops in the circuits are high. Therefore, the falling edge of the 4th flip flop will toggle the outputs of all the flip-flop, thereby changing QA and QB to 0 and QC to 1. Hence the overall output for this particular clock pulse will be 100.

This will cause the turning off of gates A1 and A2. So, when the next clock pulse arrives, then at the falling edge of the 5th clock pulse, the output of flip-flop A will again toggles from 0 to 1. So, now QCQBQA will be 101. However, this will also cause the turning on of A1 and A2.

So, when 6th clock pulse is applied then at its falling edge flip-flop A toggles from 1 to 0. And also the input to flip-flop B is high therefore, its output toggles from 0 to 1. Thus, in this case, QCQBQA will be 110.

The process further continues in this way and at the falling edge of 8th clock pulse, the output of all the flip-flops QCQBQA will reset to 000.

It is noteworthy in case of synchronous counters that the resetting of all the flip-flops in the circuit occurs at the same time. Thus the settling time of the counter is equivalent to the propagation delay time of each flip-flop in the circuit.

Thus the synchronous counter can be operated with a clock signal of high frequency.

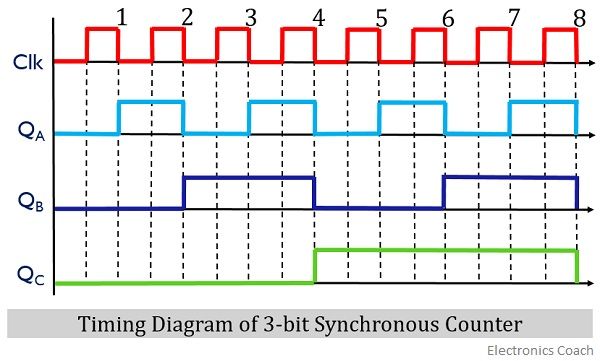

Timing Diagram of 3-bit Synchronous Counter

So, from the above explanation the truth table for the 3-bit synchronous counter is given as:

Also, the figure here shows the timing diagram of the synchronous counter:

Here in this article, we have discussed 3-bit synchronous up counter. However, one can design a down counter by simply complementing the output terminal of each flip-flop in the circuit.

Leave a Reply